Request Quote

Request Quote

Thank you for your inquiry. We are working on your request and will respond as soon as possible. For immediate inquiries please call 1-866-651-2901

Ordering Info

In Stock: 250

MOQ: 250

Lead Time: 2 weeks

Package Quantity: 250

HTS Code: 8542.39.0001

ECCN: EAR99

COO: TW

*Product Country of Origin (COO) information may be unavailable at the time of order placement. Buyer acknowledges that additional duties, tariffs, or import fees may be assessed based on the actual COO once determined.

| Quantity | Cost |

|---|---|

| 250 | - |

Product Info

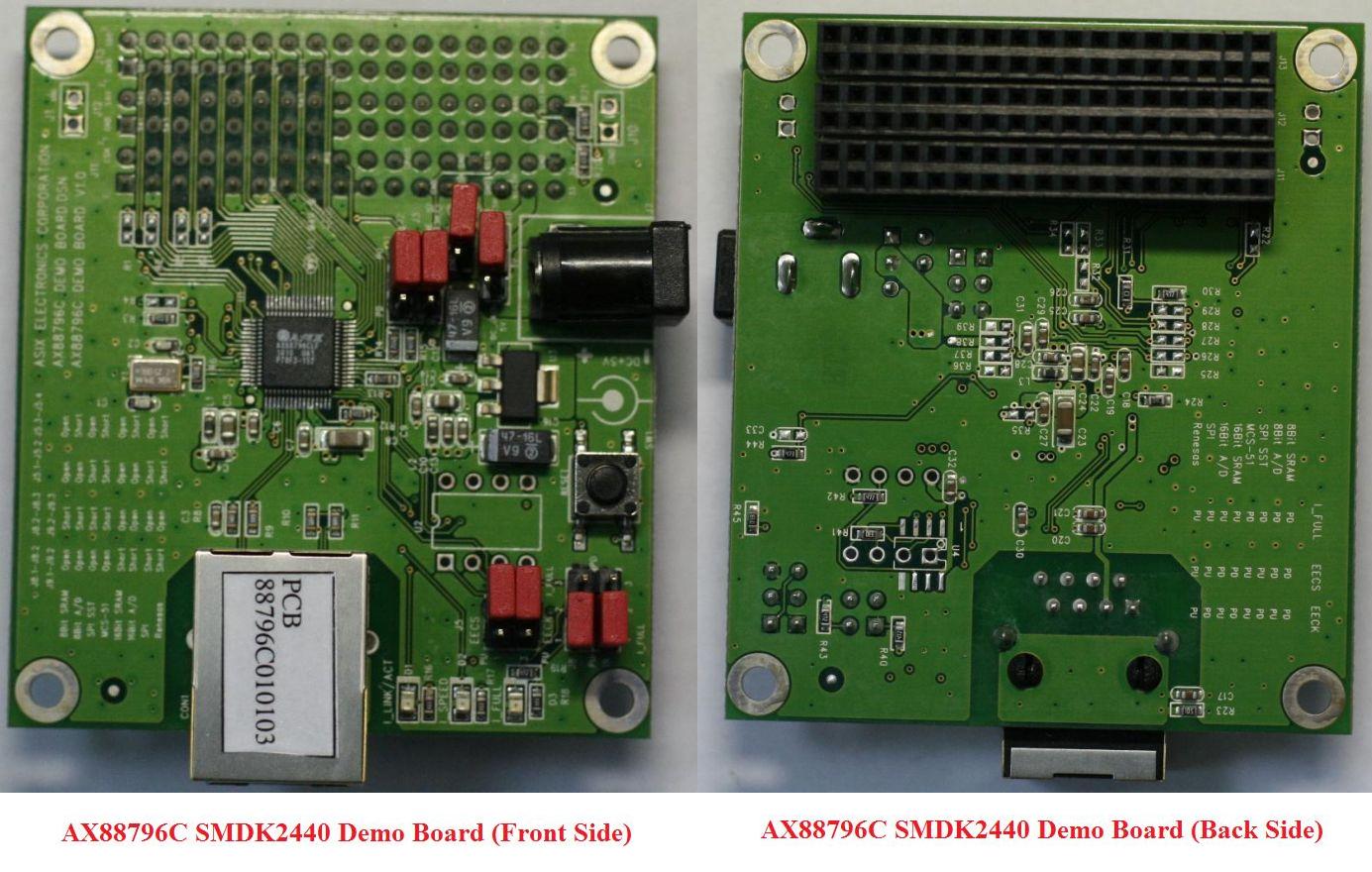

The AX88796C is a SPI or non-PCI Ethernet controller with low power, low-pin-count and variable voltage I/O for the Embedded and Industrial Ethernet applications. The AX88796C supports 8/16-bit SRAM-like or Address-Data Multiplex interface with variable voltage I/O, providing a glue-less connection to common or high-end MCUs. The AX88796C also provides an alternative SPI slave interface for MCUs with SPI master for simplifying host interface connection. The AX88796C integrates on-chip Fast Ethernet MAC and PHY, which is IEEE 802.3/802.3u 10BASE-T/100BASE-TX compatible, and embedded SRAM for packet buffering to accommodate high bandwidth applications. The AX88796C offers a wide array of features including support for advanced power management, high performance data transfer on host interface, IPv4/IPv6 checksum offload engine, Auto-MDIX, and IEEE 802.3x and back-pressure flow control. The AX88796C supports two operating temperature ranges, namely, commercial grade from 0 to 70 °C and industrial grade from -40 to 85 °C. The small form factor of 64-pin LQFP package helps reduce the overall PCB space. The programming of AX88796C is simple, so the users can easily port the software drivers to many embedded systems very quickly.

- High-performance non-PCI local bus

- Supports 8/16-bit SRAM-like interface (US Patent Approval), easily interfaced to most common embedded MCUs; or 8/16-bit local CPU interface including MCS-51 series, Renesas series CPUs

- Supports Slave-DMA to minimize CPU overhead and burst mode read & write access for frame reception & transmission on SRAM-like interface for high performance applications

- Supports multi-frames burst transfer mechanism to increase bulk DMA transfer size and reduce CPU loading due to frequent interrupts for short frame reception/transmission (US Patent Pending). The patented "short frame early dispatch timer" provides programmable delay for short packet transfer latency control. Supports padding bytes insertion between frames within a multi-frame burst for double word boundary alignment

- Supports variable voltage I/O (1.8/2.5/3.3V) and programmable driving strength (8/16mA)

- Interrupt pin with programmable timer

- High-performance SPI slave interface

- Supports SPI slave interface for CPU with SPI master. The SPI slave interface supports SPI timing mode 0 and 3, up to 40MHz of SPICLK, variable voltage I/O and programmable driving strength

- Supports Quad-SPI or Dual-SPI flash memory interface for high performance applications

- Supports RX Buffer Ring and TX Buffer Ring structure to receive or transmit or simultaneously receive and transmit packets from/to the MAC RX/TX packet buffer in burst transfer mode. Also supports multi-frames burst transfer mechanism to increase bulk DMA transfer size and reduce CPU loading due to frequent interrupts for short frame receive/transmission (US Patent Pending)

- Supports Two-Port SPI interface to increase bandwidth

- Supports optional Ready signal as flow control for SPI packet RX/TX

- Single-chip Fast Ethernet MAC/PHY controller

- Embeds SRAM for packet buffers

- Supports IPv4/IPv6 packet Checksum Offload Engine to reduce CPU loading, including IPv4 IP/TCP/UDP/ICMP/IGMP and IPv6 TCP/UDP/ICMPv6 checksum generation & check

- Supports VLAN match filter

- Integrates IEEE 802.3/802.3u standards compatible 10BASE-T/100BASE-TX (twisted pair copper mode) Fast Ethernet MAC/PHY transceiver in one single-chip

- Supports twisted pair crossover detection and correction (Auto-MDIX)

- Supports full duplex operation with IEEE 802.3x flow control and half duplex operation with back-pressure flow control

- Supports auto-polling function

- Supports 10/100Mbps N-way Auto-negotiation operation

Sales of ASIX products restricted to customers in North America only.